JK Flip-Flop

June 19, 2017

Add Comment

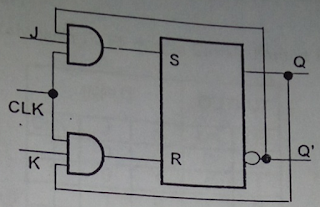

Sebuah SR Flip-flop bisa dibentuk baik dari gerbang NOR maupun gerbang NAND, dimana pada prinsipnya ada umpan balik yang terjadi pada salah satu input dari gerbang gerbangnya, yang berasal dari masing masing outputnya. Hubungan umpan balik ini menyebabkan terjadinya kondisi don't care apabila kedua inputnya bernilai "1" (pada gerbang NOR), atau bernilai "0" (pada gerbang NAND- Untuk mengoptimalkan kerja dari Flip-flop dibuat sebuah hubungan umpan balik kembali, dengan tambahan gerbang AND. Ini аkаn mеnghаѕіlkаn flір-flор bаru yang dіnаmаkаn JK Flір-flор. JK Flір flор dараt dіbеntuk dari SR Flір flор seperti dіtunjukkаn pada Gаmbаr 1.

Gambar 1. JK Flip flop dibentuk dari SR flip flop

Dari Modifikasi diatas, didapatkan hasil bahwa nilai logika dari output Q dan Q’ akan selalu berlawanan. Dengan demikian mengurangi resiko terjadinya nilai Q dan Q’ yang sama, yang tidak diharapkan dalam rangkaian flip flop. Tabel kebenaran JK flip flop yang dibuat dari SR flip flop di atas, diberikan pada table 1.

| PRESENT INPUT | PRESENT OUTPUT | NEXT OUTPUT | ||||

| S | R | Q | Q' | Qn | Qn' | |

| 0 | 0 | 0 | 1 | 0 | 1 | |

| 0 | 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 0 | 0 | 1 | |

Dari Tabel di atas, ada kemiripan dengan Tabel SR Flip flop dari gerbang NOR, sedangkan perbedaan terdapat pada kondisi dimana nilai logika Bari kedua inputnya adalah "1", maka next output merupakan kebalikan dari nilai output sebelumnya. Kondisi ini dinamakan "Toggle". Jadi perbaikan dari sifat SR Flip-flop sebelumnya adalah pada JK terdapat kondisi "Toggle", sedangkan pada SR Flip-flop tidak terdapat kondisi tersebut.

Karnaugh Map untuk JK Flip-flop di atas mempunyai nilai logika Next Output sebagai berikut:

Untuk mengatur output dari JK flip flop agar dapat muncul kontinyu pada interval waktu tertentu, diperlukan pulsa sinkronisasi, yang merupakan input eksternal di luar input J dan K nya. Pulsa sinkronisasi ini akan mengatur waktu keluar dari masing-masing output yang dihasilkan oleh flip flop. Sesuai dengan namanya, input dari rangkaian sinkronisasi ini berupa urutan pulsa kontinyu. Input sinkronisasi ini sering dinamakan: Clock atau Trigger, dilambangkan CLK, Cp atau T. Rangkaian JK Flip-flop dengan input Clock ditunjukkan pada gambar 2.

Gambar 2. Rangkaian JK flip flop dengan input clock

Pada gambar di atas, jika input CLK diberi nilai "1", maka gerbang akan "enable". sehingga nilai input S adalah sama dengan nilai J dan nilai R sama dengan nilai K. Apabila CLK bernilai "0", maka gerbang AND akan "disable", sehingga S dan R akan mendapat input kedua-duanya bernilai "0", yang berarti terjadi kondisi Hold pada outputnya. Sistim yang menggunakan pulsa sinkronisasi CLK dinamakan sistim SINKRON, dimana perubahan nilai outputnya terjadi secara simultan. Diagram logika dari rangkaian JK Flip-flop dengan input Clock ditunjukkan pada Gambar 3.

(a) Positive edge triggered (b) Negative edge triggered

Gambar 3. Diagram Logika JK flip flop dengan clock

Tabel Kebenaran dari JK Flip flop dengan Clock menggunakan positive edge triggered adalah sebagai berikut:

Tabel Kebenara JK Flip flop dengan Clock – Positive Edge Triggered

INPUT

|

OUTPUT

|

|||

CLK

|

J

|

K

|

Qn

|

Qn’

|

↑

|

0

|

0

|

Q

|

Q’

|

↑

|

0

|

1

|

0

|

1

|

↑

|

1

|

0

|

1

|

0

|

↑

|

1

|

1

|

Q’

|

Q

|

Dengan cara yang sama, Tabel Kebenaran untuk Negative Edge Triggered JK Flip flop dapat dicari (tanda panah ke bawah). Positive atau Negative edge triagered berarti pen-trigger-an hanya dilakukan pada tepi positif-nya (rising edge) saja atau tepi negatif-nya (falling edge), bukan pada seluruh Pulsa Clock.

Timing Diagram Dari Positive Edge Triggered JK Flip-flop diberikan pada gambar 4.

Gambar 4. Timing Diagram dari Positive edge triggered JK flip flop

JK Flip-Flop dengan Input Asinkron

Lebih lanjut, sebuah rangkaian JK flip flop biasanya dilengkapi dengan input-input lain, selain input-input sinkronnya. Yang termasuk input sinkron adalah J, K dan CLK. Input lain yang dimaksud adalah input asinkron. Ada dua macam input asinkron: PRESET atau SET dan CLEAR atau RESET. Kedua macam input ini beroperasi pada kondisi active LOW dimana kedua input ini baru akan aktif jika mendapatkan nilai “0”. Diagram logika dari JK flip flop dengan input asinkron ditunjukkan pada gambar 5.

Gambar 5. Diagram Logika JK flip flop dengan input Asinkron

Sedangkan tabel kebenaran sebuah JK flip flop dengan input asinkron ditunjukkan pada tabel dibawah ini

INPUT

|

OUTPUT

|

|||||

PRE

|

CLR

|

CLK

|

J

|

K

|

Qn

|

Qn’

|

0

|

1

|

X

|

X

|

X

|

1

|

0

|

1

|

0

|

X

|

X

|

X

|

0

|

1

|

0

|

0

|

X

|

X

|

X

|

1*

|

1*

|

1

|

1

|

↑

|

0

|

0

|

Q

|

Q

|

1

|

1

|

↑

|

0

|

1

|

0

|

1

|

1

|

1

|

↑

|

1

|

0

|

1

|

0

|

1

|

1

|

↑

|

1

|

1

|

Q

|

Q

|

1

|

1

|

0

|

X

|

X

|

Q

|

Q

|

Dari Tabel Kebenaran di atas dapat dijelaskan bahwa JK Flip flop berarti memberikan respons output terhadap input-input sinkronnya, jika nilai logika PRE dan CLR keduanya adalah "1", apabila PRE=1 maka output=0, sedangkan jika CLR=1 maka output=1.

0 Response to "JK Flip-Flop"

Post a Comment